기본 요소 - Processor(CPU), Main Memory, System bus, I/O modules

Processor (CPU): ALU(Arithmetic Logic Unit), CU(Control Unit), Register로 구성

- ALU: 연산 담당

- CU: 컨트롤

- Register: 매우 작지만 CPU 안에 있어서 접근 속도 빠름, 연산을 위한 저장 공간

1. data I/O registers: CPU와 메모리 간 데이터를 주고 받기 위함

- Memory address register (MAR); 메인 메모리에 대한 주소

- Memory buffer register(MBR); 메인 메모리에 대한 버퍼

=> MAR에 적힌 주소에 MBR에 적힌 데이터를 LOAD(read)/STORE(write)

- I/O address register, I/O buffer register

2. Control and status registers: CPU 동작 제어 및 연산 상태 저장

- Program Counter(PC): 다음에 가져와야 할 명령어의 주소 저장

- PC는 프로그램 시작 시 첫 명령어의 주소를 가리킴

- 실행마다 값 1씩 증가

- Instruction Register(IR): 프로그램 코드가 기계어로 변환되었을 때 instructions는 크게 4가지 중 하나임

- Processor-memory 간 데이터 주고받는 명령어

- Processor-I/O device 간 데이터 주고받는 명령어

- Data processing 명령어: +, - 등 실제 연산

- Control 명령어: JUMP 등

=> CPU가 PC에서 주소를 가져와, 그 주소로 이동해서 명령어를 가져와서 IR에 넣음

* CPU 명령어 실행 과정

- Fetch: CPU가 PC에 적힌 주소의 명령어를 IR에 넣는 과정

- Execute: 실행

- Program Status Word(PSW)

- Condition codes: 명령어 실행 결과 저장, 문제가 발생했을 때 빠르게 대처하기. 위함

- Interrupt enable/disable: 인터럽트 허용 여부 저장

- Supervisor/user mode: 현재 수행하는 코드가 사용자가 짠 코드인지, 운영체제 코드인지

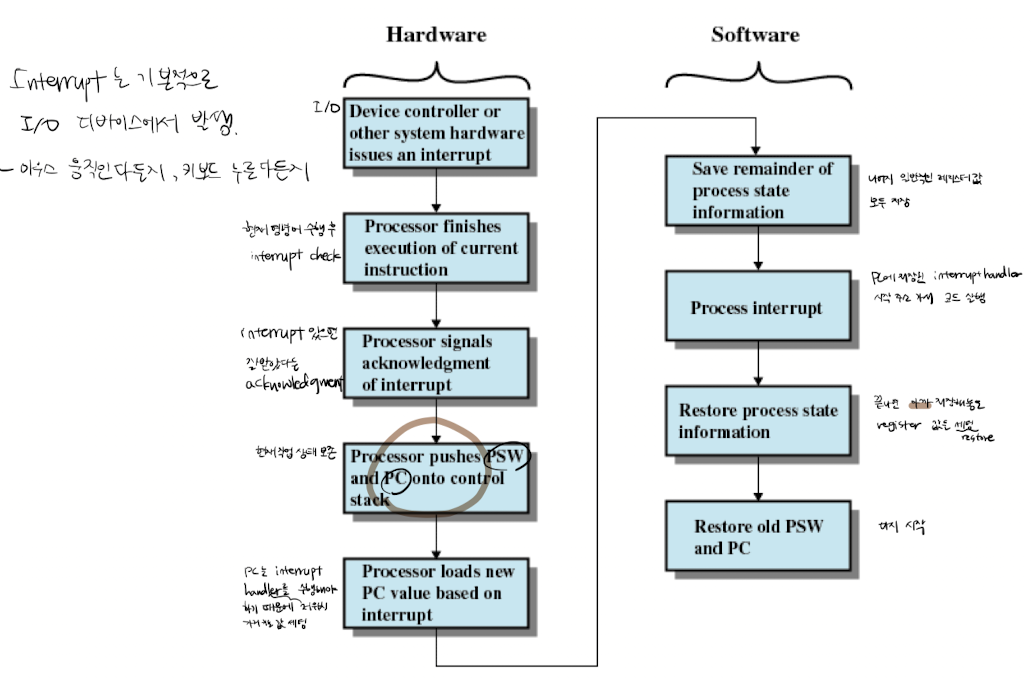

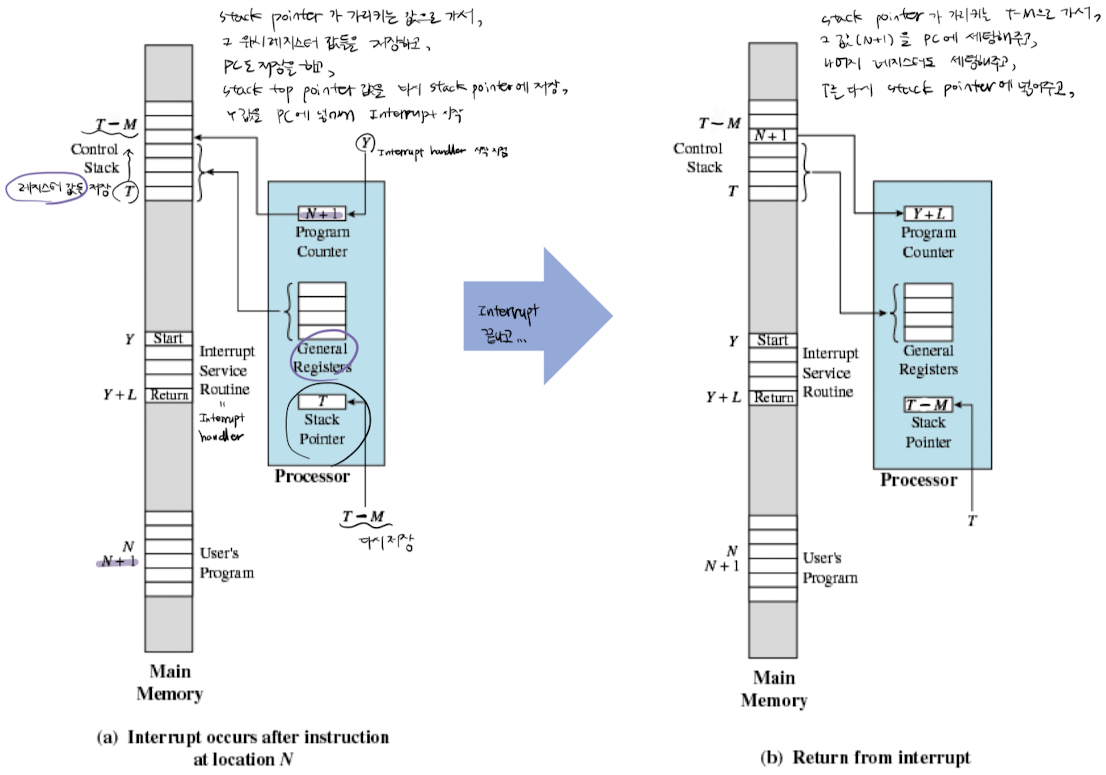

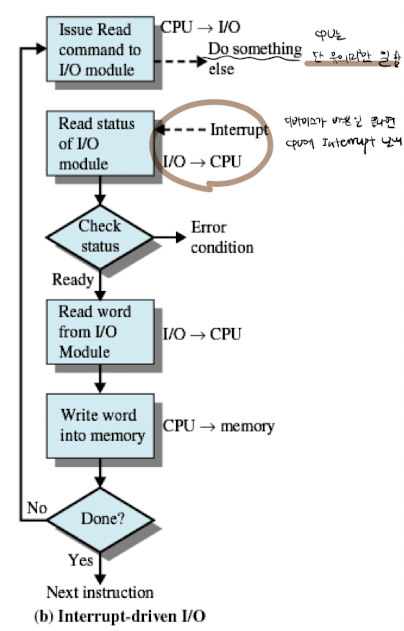

Interrupt: CPU가 현재 실행 중인 fetch-execute 과정을 멈추고 해야 하는 일이 생길 때의 매커니즘

ex) 동영상 보고 있는데 마우스 커서 움직이는 경우

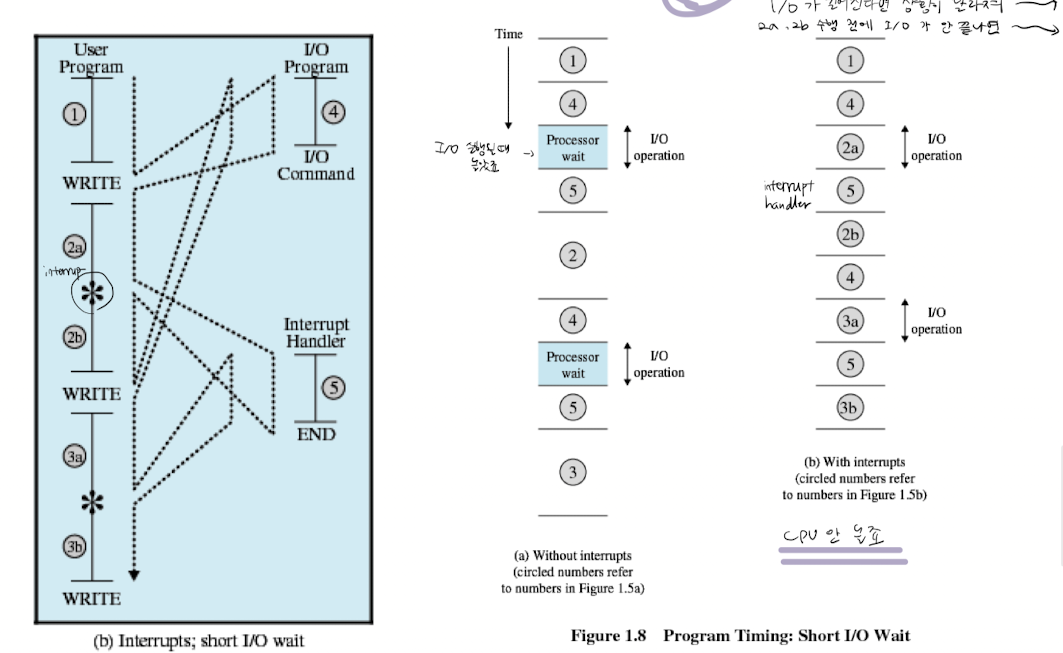

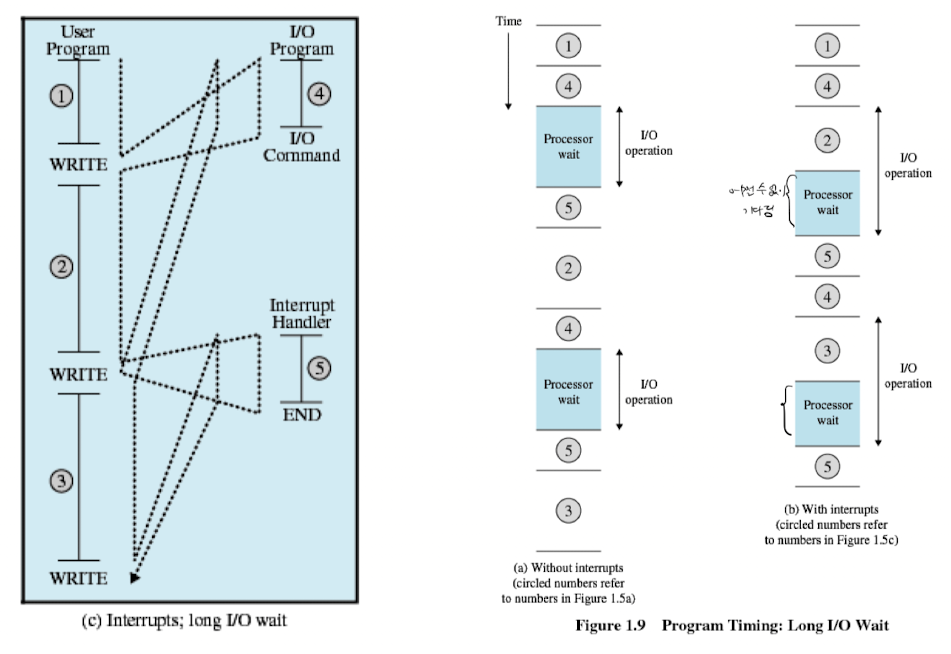

- I/O 장치는 매우 느리기 때문에 기다리면 개손해, CPU는 interrupt 넘겨놓고 다른 일을 할 수가 있음

Simple Interrupt Processing

Interrupt 전 현재 상태 보존 과정

Program Flow with Interrupts: Short I/O Wait

Program Flow with Interrupts: Long I/O Wait

-> I/O는 많이 느리기 때문에 최적화를 위해 순서를 바꾸는 경우 생김

3. User-visible registers: 코드 내에서 어셈블리로 레지스터에 사용자 직접 접근 가능

나머지 레지스터는 운영체제를 통해 접근 가능

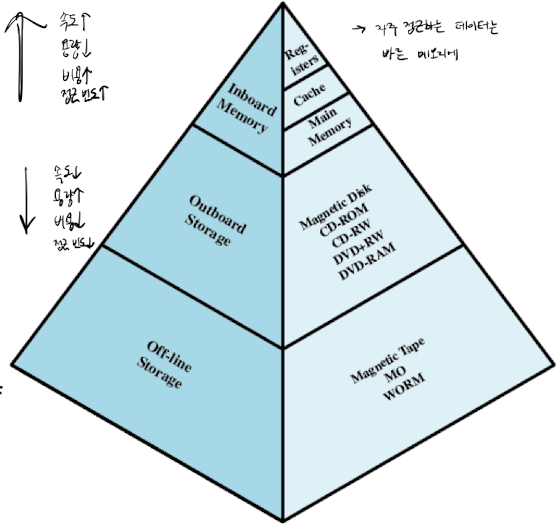

Main Memory: 휘발성, 전기가 나가면 데이터가 사라져버리는, 무척 빠르기 때문에 주기억장치로 사용

Locality of reference(참조 지역성): 모든 데이터를 균일하게 접근하지 않고 특정 데이터, 명령어들을 빈번하게 접근하더라~

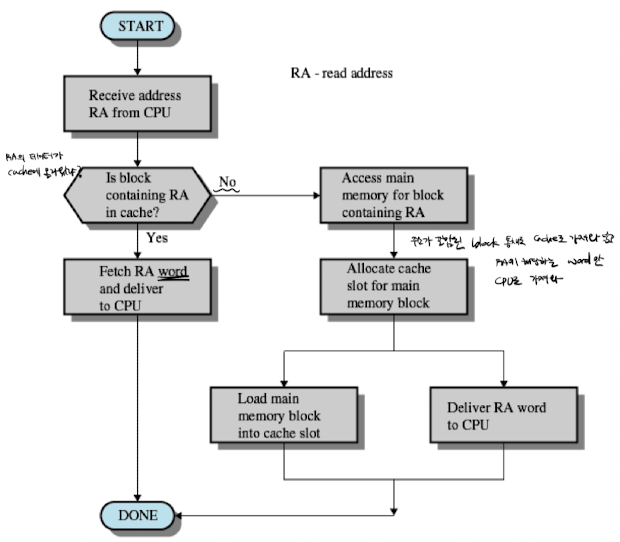

Cache

필요성: CPU와 DRAM 간 속도 차를 줄일 필요가 있겠구나

- 메모리의 속도 때문에 CPU의 명령어 실행 속도가 제한될 수밖에 없다는 걸 해결하기 위해 DRAM보다 훨씬 빠른 SRAM 사용

- 가격은 비싸고 용량은 적지만 속도가 빠름

Cache Design

- 자주 접근되는 놈이 전부 다 캐시에 올라가면 좋겠지?

ㄴ> 얘의 크기가 그렇게 크지 않아서 캐시의 크기가 그렇게 크지 않아도 효과가 굳

- Block 단위로 한 번에 많은 범위를 캐시로 올렸다 내렸다 해서 메모리 접근 횟수를 줄일 수 있음

- Mapping function: 캐시는 메모리가 아니기에 주소로 찾아갈 수 없음 -> 빠르게 찾기 위한 수단 필요, 알고리즘

- Replacement algorithm: 캐시 꽉 차면 block 버려야 함

LRU(Least-Recently-Used) 알고리즘; 방금 사용된 놈이 또 사용되겠다는 상식적 아이디어

- Write policy: 만약 캐시에만 STORE(write)하면 메모리와 달라짐 -> 심각한 문제

Disk Cache

DRAM 사용, 메모리와 하드 디스크 간 속도 차 -> 하드 디스크 접근 줄여야

System bus: CPU, 메모리, I/O modules가 데이터를 주고받는 통로

I/O modules: 주변 장치

I/O: 메모리와 버퍼 사이의 입출력

ㄴInput: 컨트롤러 안의 버퍼에 있는 데이터를 메모리로 가져오는 것

ㄴOutput: 메모리에 있는 데이터가 컨트롤러의 버퍼로 나가는 것

디바이스가 메모리에 직접 접근하지 못해 CPU가 word 단위로 Loop를 돌아야 해서 비효율적임

=> Direct Memory Access(DMA); CPU가 아닌 신뢰할 수 있는 다른 장치(I/O 장치 X, 믿을 수 없음)가 메모리에 직접 접근할 수 있도록 함

- DMA 컨트롤러(I/O를 담당하는 별도의 장치)가 CPU가 하던 일을 독립적으로 알아서 함

Multiprogramming

CPU가 할 일이 있는데도 놀면 죄악, 하나의 프로그램만 수행하기 때문에 생기는 문제

-> 여러 프로그램 동시 실행

- Interrupt오면 다른 프로그램 실행

- 우선순위가 높은 프로그램 먼저 실행 => CPU 스케줄링

- 단, interrupt 수행이 끝나고 원래의 프로그램으로 돌아간다는 보장이 없음. 관리는 복잡해지지만 어쨌든 일만 하면 되니까 효율성을 높임

컴퓨터 부팅 과정

운영체제 안 깔아도 기본 동작 ㅇ -> bootstrap 프로그램(read only 메모리에 박혀있고, 메인보드에 존재)이 장치 initialize, os kernel 탑재함

한양대학교 강수용 교수님 운영체제 강의 내용 정리

'운영체제' 카테고리의 다른 글

| [운영체제] Process synchronization (2) (0) | 2024.03.06 |

|---|---|

| [운영체제] Process Synchronizationtion (1) (0) | 2024.02.27 |

| [운영체제] CPU Scheduling (3) | 2024.02.20 |

| [운영체제] Process and Threads (2) | 2024.02.09 |

| [운영체제] Operating System Overview (0) | 2024.01.23 |